# Carbon Nano Tube Field Effect Transistor based BBL-PTL full adders with level restorer structures

Srilatha Koteswara, Ishwarya Punati and Avireni Srinivasulu<sup>‡</sup>, SM-IEEE

Department of Electronics and Communication Engineering

V. F. S. T. R University (Vignan's University), Vadlamudi, Guntur, Andhra Pradesh, India

Email: avireni\_s@yahoo.com (or) avireni@ieee.org

Received 1 June 2016, Revised 23 Aug 2016, Accepted 13 Sep. 2016

Full Adder (FA) is an important component not only in arithmetic circuits, but also in designing and development in all types of processors. The performance parameter of the one bit full adder has been implemented to increase the speed of the system. In this paper two Carbon Nano Tube Field Effect Transistor (CNTFET) based level restorers are introduced to the sum circuit of the branch-based logic and pass transistor (BBL-PT) full adder. The proposed level restorers eliminate the existence of voltage step which is presented in the conventional full adder [1]. T.V.Rao *et. al* proposed level restorer circuits that have used +1.2 V supply rail voltage [2]. By using these level restorers we could able to achieve good delay performance. The proposed 1-BIT full adder is graded high as it has less power consumption with the conventional 1-BIT full adders. The performance of the proposed CNTFET based BBL-PT FA with new level restorer structures are examined using Cadence with 32 nm CNTFET technology files with a supply rail voltage of +0.8 V.

**Keywords:** CNTFET; Branch-based logic; Pass transistor logic.

#### 1. INTRODUCTION

Adders are supposed to be an important components in each and every processor architecture. Generally, intensive research has been carried out to implement adders in different architectures, configurations, layouts, design styles and design methodologies. All these are implemented with the main purpose of improving adder speed and energy efficiency. Its speed mainly depends upon the delay, power consumption and power delay product. There also exist some conventional full adder structures and one amongst them is CMOS logic with 28 transistors and the other is PTL logic with 26 transistors. From this there arises large input capacitance but it cannot provide high speed operation. Another FA is Complimentary Pass Transistor Logic (CPL) with 32 transistors, but due to possessing a large number of internal

nodes and static inverters, it consumes a lot of power while it acquires high speed and full swing design [1-6].

In this paper Pass Transistor Logic (PTL) is used to sum and branch based logic (BBL) to carry. There are many advantages in using this logic. It has simpler characterization and no diffusion interruption; moreover, it has a common drain for two branches with less number of contacts. The style in this design is mostly used to decrease parasitic capacitances [7-9]. From this, it achieves low power and also advantageous to acquire high speed. The major disadvantage is the voltage step that exists [1] to correct it; we can also use level restorers for the same purpose. In this paper this logic is implemented by using CNTFETs because of their advantages. It has more benefits while compared to the traditional MOSFET silicon based structure. CNTFETs have better control over channel formation. It has high electron mobility, high electron density and high transconductance when compared to traditional MOSFETs. Moreover, its threshold voltage and sub threshold slope is better than traditional MOSFETs [10-19].

Carbon Nano Tube (CNT) has gained popularity in the past few years for its tiny dimensions, special morphologies and also its potential implementing application in many emerging technologies. One of the examples of emerging technologies is cutting edge with in nanotechnology. It is capable of high efficiency and used in a wide range of applications in many streams of science and technology. CNTFETs consumes less power and proves much faster than the existing silicon based FETs [20].

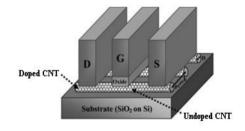

A tube shaped material is a carbon nano-tube which is fabricated from carbon. By using the nanometer scale its diameter can be measured. These are fabricated from the graphite layer. Then the graphite sheet forms into a rolled up continuous, unbroken hexagonal mesh. These are the members of the fullerene family. These are long and hollow structures which appear to be containing one atom thick sheet of carbon called graphene [21]. Fig. 1(a) presents the schematic of cross sectional view and Fig. 1(b) top view CNTFET [22], [23].

(a) Cross sectional view

Figure. 1: Schematic diagram of CNFET device.

CNTFETs are the next alternatives to the MOSFETs. These are said to be the molecular devices which prevent the fundamental silicon restriction in the ballistic transport. One of the CNTFET feature is their geometry that depends on threshold voltage. CNTFETS provides more advantages rather than silicon based technologies [24], [25].

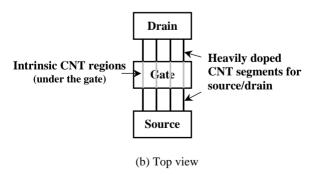

These are four terminal devices comprising of a nano-tubes acting as conducting channel, linking the source and drain contacts. According to the operation CNTFETs can be divided into two categories. They are Schottky Barrier CNTFET (SB-CNTFET) shown in Fig 2.(a) and MOSFET-like FET shown in Fig 2.(b) [26-30]. The conductivity of the Schottky Barrier CNTFET is regulated through the majority carriers tunneling over the Schottky barriers on the terminal contacts. The SB-CNFET on-current is achieved through the contact resistance. The Schottky Barriers placed at source/drain contacts are owing to the Fermi-level positioning of the metal and semiconductor interface. The height plus width of the Schottky Barriers, and consequently the conductivity, are tuned by the gate electrostatically. SB-CNFET presents the ambipolar conveying style. MOSFET like CNFET, exhibits the unipolar behavior by concealing either electron (p-CNTFET) or hole (n-CNTFET) transport with extrinsic source and drain.

The threshold voltage of a CNTFET is gauged by (1)

$$V_{th} \approx E_{bg} / 2 e \approx 0.436 / D_{CNT}(nm)$$

(1)

where  $E_{bg}$  is the energy band gap of carbon nano-tube, e is the charge of electron,  $D_{CNT}$  is the carbon nano-tube diameter and n and m are the chirality of the CNT. It can be seen from (1) that the threshold voltage of a CNTFET is inversely related to the diameter of its nano-tubes, which is computed by (2)

Figure. 2: (a) SB-CNFET (b) MOS-CNFET

CNTFETs have proved experimentally that they have excellent current capabilities. At 32 nm feature size it has been proved that at a single device level its presence effects the related process. CNTFETs have a different band structure which causes ballistic operation. So, there is a possibility of acquiring when compared to other nanotechnologies. So, it might be the reason that it has been used in high frequency and low voltage application devices. In CNFETS they have been classified into p-FET and n-FET devices and these devices are of the same size and have the same mobility. The current driving capability of transistor in sizing of complex circuits is also the same. To turn ON a CNTFET device, it requires a minimum threshold voltage and this voltage can be adjusted by changing the chiralities of CNT's. It makes the device more flexible when compared to the MOSFET. To achieve the required performance, it has to be operated under low voltage [31-41].

The remaining section of this paper is arranged as follows. Firstly, the proposed adders structure followed by its implementation and then its simulated results, finally it has ended up in conclusion.

#### 2. Proposed circuits and operation

A full adder is a combination of its 3-inputs. The relation between the input and output can be expressed as

$$Sum = ABC_{in} + \overline{ABC}_{in} + \overline{ABC}_{in} + A\overline{BC}_{in}$$

(3)

$$Carry = A.B + B.C_{in} + A.C_{in}$$

(4)

In this circuit by using minimum number of transistors and their intra connections; we can attain the low power consumption. Using the unsophisticated characterization makes the circuit very advantageous. This can be achived by branch based logic. It has many utilities that can be considered. It overcomes the diffusion capacitance that occurs in the circuit. So, by stepping in its foot prints it is found more advantageous in attaining low power and high speed.

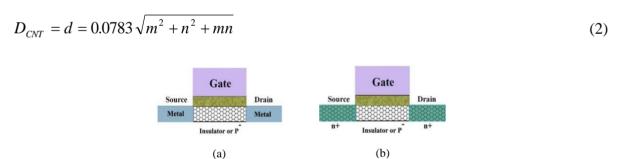

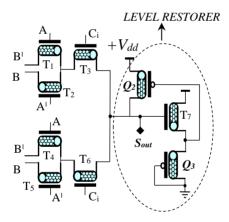

## 2.1. CNTFET based proposed full-adder structure-I

The main disadvantage in this full adder is that it gives the weak output in the pass transistors. This cannot be accomplished by giving feedback to pull up as p-CNTFET transistor to sum block. To overcome this situation, it has to be made to supply sufficient drive in its subsequent stages. When a voltage step exists in the output node by  $0 \to 1$  transition it can be used. This voltage drop and the delay that occurred in the level restores can be used to renew the weak logic '1' level. For the effected voltage step ON and OFF timings might not be equal. So to overcome this, the proposed adder should contain level restorers.

Figure. 3: CNTFET based full adder with level restorer structure-I (within the dashed circle).

Here, in the circuit shown in Fig 3(a), it posses' n-CNTFET transistors from  $T_1$  to  $T_6$ . While coming to the level restorer circuit,  $T_7$  CNTFET where its gate is connected to the supply. For this n-channel transistor is always in ON condition. There exists only a p-CNTFET

$(Q_1)$  which acts as a pull up for the network. So this type of methodology gives us high voltage gain.

When the voltage at node " $S_{out}$ " is  $< V_{dd}/2$ , the n-CNTFETs ( $T_8$ ) in the restorer will not reach switching threshold and therefore turned OFF. The resultant output of  $T_7$  and  $T_8$  CNTFETs is logic '1'. This logic '1' is the input to the pull-up p-CNTFETs ( $Q_1$ ) and then pull-up  $Q_1$  is turned OFF. The node " $S_{out}$ " is charged with an effective drive current that equals the current of the n-CNTFETs network.

When the voltage at node " $S_{out}$ " reaches to  $V_{dd}/2$ , the n-CNTFETs ( $T_8$ ) in the restorer is turned ON. Then, the p-CNTFETs ( $Q_1$ ) is turned ON and the effective drive current charging the capacitance at node " $S_{out}$ " becomes the sum of the current flowing through the n-CNTFETs network and the pull-up p-CNTFETs ( $Q_1$ ) currents.

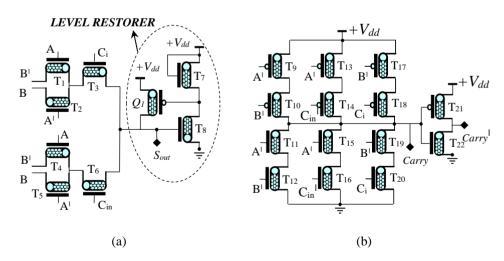

## 2.2. CNTFET based proposed full-adder sum structure-II

In the second proposed CNTFET full adder sum circuit is shown in Fig. 4 and the carry circuit is shown in Fig. 3(b). When logic '1' is applied to the input of n-CNTFET network  $T_1$  to  $T_6$  shown in Fig. 2, then the logic '1' is passed through the n-CNTFET network, the node "S<sub>out</sub>" is to be charged to a weak logic '1'. When the voltage at node "S<sub>out</sub>" is  $< V_{dd}/2$ , the n-CNTFET ( $T_7$ ) in the level restorer is turned OFF, the p-CNTFET ( $T_7$ ) is always in ON condition irrespective of the applied input; then the output of inverter becomes logic '0'. The output of the  $T_7$  and  $T_7$  and  $T_7$  cNTFETs is logic '0', it is applied to the input of pull-up p-CNTFET ( $T_7$ ), then the pull-up p-CNTFET ( $T_7$ ) is turned ON, and the node " $T_7$  is charged with an effective drive current that equals the current of the n-CNTFET network.

Figure. 4: CNTFET based proposed full adder sum circuit level restorer structure-II (within the dashed circle).

When the voltage at node " $S_{out}$ " reaches to  $V_{dd}/2$ , the n-CNTFET ( $T_7$ ) in the level restorer is turned ON, then the p-CNTFET ( $Q_3$ ) is always in ON condition irrespective of its applied input; then the output of inverter is logic '1'. The output of the  $T_7$  and  $Q_3$  CNTFETs is logic '1', it is applied to the input of pull-up p-CNTFET ( $Q_2$ ), then the pull-up p-CNTFET ( $Q_2$ ) is turned OFF, and the node " $S_{out}$ " is charged with an effective drive current that equals the current of the n-CNTFET network. The carry circuit shown in Fig 3(b) is the same for both of the proposed full adders. In carry circuit complimentary logic is used where it can be classified as N-CNTFETs and P-CNTFETs. It is composed of branch based logic where all the transistors are connected in series. Finally, the expression can be obtained by using the k-maps.

$$Sum = A \oplus B \oplus C_{in}$$

$$Carry = A.B + C_{in}.(A + B)$$

(5)

(6)

## 3. Simulation Results

6.

7.

The proposed 1-BIT CNTFET based full adders with modified level restorers are simulated by using Spectre Cadence with 32 nm CNTFET technology files [28]. The circuits simulated on Cadence tool have been carried out with supply voltage  $V_{dd} = +0.8 \text{ V}$  and frequency of f = 100 MHz. The design parameters and chirality values of Fig. 3 and Fig. 4 CNTFETS are shown in the Table. 1 below.

Table 1: 32 nm Stanford Model Technology Parameters.

S.No **CNTFETS** Chiralities 1.  $Q_1, Q_2, Q_3$ (11, 0)2.  $T_1 - T_{22}$ (19, 0)3. Physical Channel Length 32 nm 4. Oxide thickness 4 nm 5. Dielectric Constatnt 16

Power Supply

Threshold Voltage

Chiralities of Fig. 3 and Fig. 4

0.8 V

0.49

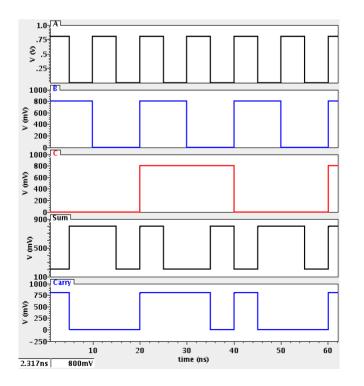

**Figure. 5**: Simulated input & output waveforms of full adder with level restorer structure-I of Fig. 3.

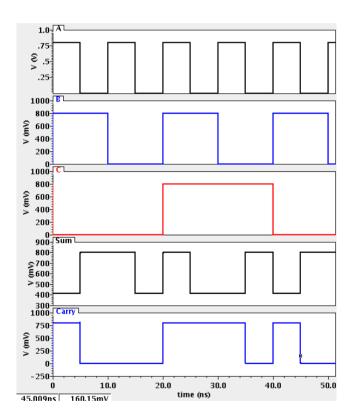

The simulated input and output waveforms of the proposed adders Fig. 3 and 4 are shown as above in Fig. 5 and Fig. 6. The simulated total power consumption of Fig. 3 is 0.1395  $\mu w$  and Fig. 4 is 0.142  $\mu W$ .

In the BBL-PT full adder, there existed a voltage step in the sum output waveform during  $0 \rightarrow 1$  transition [1] and the same was eliminated in the T.V. Rao *et. al* proposed full adder designs using current sink inverter and current source inverter with the supply rail voltage of +1.2 V [2]. The voltage step in BBL-PT is due to the delay needed by the level restorer to restore the weak logic '1' level. The proposed level restorers shown in Fig. 3(a) and Fig. 4 does not require delay to restore the weak logic '1' level. In Fig. 3 and 4, the inputs (A, B & C) applied for all possible combinations i.e. 000 to 111.

In the Table. 2 shown as under the candidate's design has been compared with the supply voltages and the proposed circuits also proved consuming less power.

**Figure. 6**. Simulated input & output waveforms of full adder with level restorer structure-II of Fig. 4.

Table 2: Comparison of earlier published full adder circuits with supply rail voltage

| Reference number       | Type of transistors used | Supply voltage (V) |

|------------------------|--------------------------|--------------------|

| I. Hassoune et. al [1] | MOSFETs                  | +1.2               |

| T. V. Rao et. al [2]   | MOSFETs                  | +1.2               |

| D.Radhakrishnan [3]               | MOSFETs | +3   |

|-----------------------------------|---------|------|

| D. Datta et. al [4]               | MOSFETs | +2.5 |

| Y. S. Mehrabani et. al [5]        | CNTFETs | +0.9 |

| S. R. Prasad et. al [6]           | CNTFETs | +0.9 |

| Proposed circuits Fig. 3(a) and 4 | CNTFETs | +0.8 |

### 5. Conclusion

In this paper, two CNTFET based BBL-PT full adders with level restorers are presented. Two new circuits decrease the existing diffusion capacitances and also eliminate the voltage step. The designed full adder circuits attain less power consumption when compared to the traditional MOSFET. Hence, these circuits can be implemented in many applications such as ripple carry adder, multipliers, ALUs etc.

#### References

- [1] I. Hassoune, D. Flandre, Ian O' Connor and Jean-Didier Legat, ULPFA: A new efficient design of a power-aware full adder, IEEE Transactions on Circuits and Systems-1: Regular papers, **57** (2010), 2066-2074.

- [2] T. V. Rao and Avireni Srinivasulu, Modified level restorers using current sink and current source inverter structures for BBL-PT full adder, Radioengineering, **21** (2012) 1297-1286.

- [3] D. Radhakrishnan, Low-voltage low-power CMOS full adder, IEE Proc. Circuits Devices Syst, **148** (2001) 19-24.

- [4] D. Datta and Debarshi Datta, A novel power efficient N-MOS based 1-bit full adder, 2016 International Conference on Microelectronics, Computing and Communications (MicroCom), 2016 (1 5), DOI: 10.1109/MicroCom.2016.7522561.

- [5] Y. Safaei Mehrabani, and M. Eshghi, Noise and Process Variation Tolerant, Low-Power, High-Speed, and Low-Energy Full Adders in CNFET Technology, IEEE Transactions on Very Large Scale Integration (VLSI) Systems, **PP** (9) (2016) 1-14. DOI: 10.1109/TVLSI.2016.2540071.

- [6] S. R. Prasad, Y. P. Sai and S. Naga Leela, Low leakage CNTFET full adders, in Proc. of 2015 Global Conference on Communication Technologies (GCCT), (2015) 174 - 179, DOI: 10.1109/GCCT.2015.7342647

- [7] R. Kumar and V. K. Pandey, A New 5-Transistor XOR-XNOR circuit based on the pass transistor logic, IEEE World Congress on Information and Communication Technologies, (2011) 667 671.

- [8] A. Srinivasulu, and K. Sivadasan, "Optical Exclusive-OR Gate", Journal of Microwaves, Optoelectronics and Electromagnetic Applications, **3** (1) (2003) 20-25. ISSN: 1516-7399, ISSN: 2179-1074.

- [9] Y.-B Kim, Challenges for nanoscale MOSFETs and emerging nanoelectranics, IEEE Trans. Electr. Electron. Mater, **11**(3) (2010) 93-105.

- [10] Patcha Kavitha, M. Sarada, K.Vijayavardhan, Y. Sudhavani and Avireni Srinivasulu, Carbon nano tube field effect transistors based ternary Ex-OR and Ex-NOR gates, Current Nanoscience, **12** (4) (2016) 1-7.

- [11] I. Bejenari and M. Claus, Electron Back Scattering in CNTFETs, IEEE Transactions on Electron Devices, **63** (3) (2016) 1340 1345.

- [12] M. H. Moaiyeri, R. Faghih Mirzaee, K. Navi and A. Momeni, Design and analysis of a high-performance CNFET-based Full Adder, Int. J. Electronics, **99** (1) (2012) 113-130.

- [13] M. R. Reshadinezhad, M. H. Moaiyeri and K. Navi, An Energy-Efficient full adder cell using CNFET Technology, IEICE Transactions on Electronics, **E95**-C(4) (2012) 744-751.

- [14] K. Navi, H. Hossein Sajedi, R. Faghih Mirzaee, M. H. Moaiyeri, A. Jalali and O. Kavehei, High-Speed Full Adder Based on Minority Function and Bridge Style for Nanoscale, Integration The VLSI Journal (Elsevier), **44** (3) (2011) 155-162.

- [15] M. H. Moaiyeri, K. Navi and O. Hashemipour, Design and Evaluation of CNFET-based Quaternary Circuits, Circuits, Systems, and Signal Processing, **31** (5) (2012) 1631–1652.

- [16] J. Liang, L. Chen, J. Han, and F. Lombardi, Design and Evaluation of Multiple Valued Logic Gates Using Pseudo N-Type Carbon Nanotube FETs, IEEE Transaction on Nanotechnology, **13** (4) (2014) 695 708.

- [17] K. Navi, M. Rashtian, A. Khatir, P. Keshavarzian, O. Hashemipour, High speed capacitor–inverter based carbon nanotube full adder, Nanoscale Res. Lett., **5** (5) (2010) 859–862.

- [18] M. H Moaiyeri, A. Doostaregan, K. Navi, Design of energy-efficient and robust ternary circuits for nanotechnology, IET Circuits Devices Syst., **5** (4) (2011) 285–296.

- [19] P. Keshavarzian, K. Navi, Efficient carbon nanotube galois field circuit design, IEICE Electron. Express, **6** (9) (2009) 546–552.

- [20] M. Ossaimee, S. Gamal and A. Shaker, Gate dielectric constant engineering for suppression of ambipolar conduction in CNTFETs, Electronics Letters, **51** (6) (2015) 503 504.

- [21] S. Mothes, M. Claus and M. Schröter, Toward Linearity in Schottky Barrier CNTFETs, IEEE Transactions on Nanotechnology, **14** (2) (2015) 372 378.

- [22] J. Deng and H.-S.P Wong, A Compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application part i: model of the intrinsic channel region, IEEE Trans. Electron Devices, **54** (12) (2007) 3186–3194.

- [23] J. Deng, H. S. P. Wong, A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application part ii: full device model and circuit performance benchmarking, IEEE Trans. Electron Devices, **54** (12) (2007) 3195-3205.

- [24] M. Schröter, M. Haferlach, A. Pacheco-Sanchez, S. Mothes, P. Sakalas and M. Claus, A Semiphysical Large-Signal Compact Carbon Nanotube FET Model for Analog RF Applications, IEEE Transactions on Electron Devices, **62** (1) (2015) 52 60.

- [25] G. Cho and F. Lombardi, Circuit-Level Simulation of a CNTFET With Unevenly Positioned CNTs by Linear Programming, IEEE Transactions on Device and Materials Reliability, **14** (1) (2014) 234 244.

- [26] A. Javey, J. Guo, D. B. Farmer, Q. Wang, E. Yenilmez, R. G. Gordon, M. Lundstrom, H. Dai, Self-Aligned Ballistic Molecular Transistors and Electrically Parallel Nanotube Arrays, Nano Letters, **4** (2004) 1319-1322.

- [27] A. Javey, R. Tu, D. B. Farmer, J. Guo, R. G. Gordon and H. Dai, High Performance N-Type Carbon Nanotube Field-Effect Transistors with Chemically Doped Contacts, Nano Letters, **5** (2005) 345-348.

- [28] Stanford CNTFET Model, https://nano.stanford.edu/stanford-cnfet-model

- [29] A. Imran, Md. Hasan, Aminul Islam and S. A. Abbasi, Optimised design of a 32 nm CNTFET based low power Ultrawideband CCII, IEEE Transactions on Nanotechnology, **11** (6) (2012) 1100-1109.

- [30] J. W. Mintmire and C. T. White, Universal density of states for carbon nanotubes, Phys. Rev. Lett., **81** (12) (1998) 2506–2508.

- [31] J. Liang, L. Chen, Jie Han and F. Lombardi, Design and Evaluation of Multiple Valued Logic Gates Using Pseudo N-Type Carbon Nanotube FETs, IEEE Transactions on Nanotechnology, **13** (4) (2014) 695 708.

- [32] A. Raychowdhury and K. Roy, Carbon-nanotube-based voltage-mode multiple-valued logic design, IEEE Trans. Nanotechnol, **4** (2) (2005) 168-179.

- [33] P. Keshavarzian and K. Navi, Efficient carbon nanotube galo is field circuit design, IEICE Electron. Express, **6** (9) (2009) 546-552.

- [34] M. Hossein, M. Faghih, Akbar, Keivan, Omid, A universal method for designing low-power carbon nanotube FET-based multiple-valued logic circuits, IET Comput. Digit. Tech., **7** (4) (2013) 167-181.

- [35] Jie deng and H.-S. Phillip Wong, A compact SPICE model for Carbon-Nanotube Field-Effect transistors including non-idealities and its applications-Part-I: Model of the intrinsic channel region, IEEE Transactions on Electronic Devices, **54** (12) (2007) 3186-3194.

- [36] S. Lin, Y. Kim, F. Lombardi, CNTFET-based design of ternary logic gates and arithmetic circuits, IEEE Trans. Nanotechnol., **10** (2) (2011) 217-225.

- [37] M. H. Moaiyeri, A. Doostaregan, K. Navi, Design of energy-efficient and robust ternary circuits for nanotechnology, IET Circuits Devices Syst., **5** (4) (2011) 285-296.

- [38] K. You, K. Nepal, Design of a ternary static memory cell using carbon nanotube-based transistors, IET Micro Nano Lett, **6** (6) (2011) 381-385.

- [39] P. L. McEuen, M. Fuhrer, H. Park, Single-walled carbon nanotube electronics, IEEE Trans. Nanotechnol, **1** (1) (2002) 78-85.

- [40] A. Paulthurai, B. Dharmaraj, Low-power and high-performance 1-bit set full-adder, Int. J. Nanoelectronics and Materials, **6** (2) (2013) 105-111.

- [41] E. Hosseini, Propagation Effects in Carbon Nanoelectronics, Int. J. Nanoelectronics and Materials, **8** (2015) 91-98.